Processeur x86

Le CPU

Le CPU x86 (Unité de Traitement Centrale ou Central Processing Unit) est un circuit électronique destiné à traiter des valeurs binaires, à la base d’une famille de microprocesseurs créée par Intel.

Les CPU x86 sont fabriqués par de multiples fondeurs qui leur ajoutent des options et font évoluer cette famille de processeurs. Parmi eux, citons AMD qui a introduit des jeux d’instructions qui lui sont spécifiques.

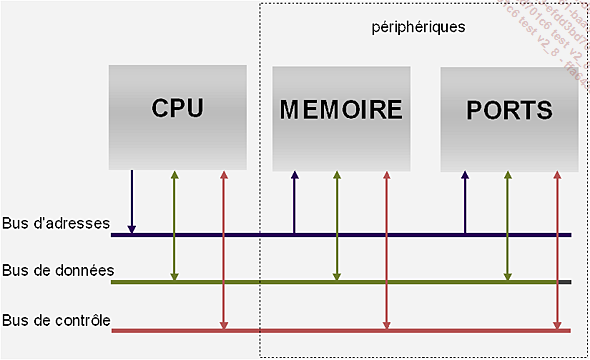

Le fonctionnement des processeurs de cette famille est basé sur l’architecture Von Neumann, soit un bus d’adresses, un bus de données et un bus de contrôle.

On appelle cette architecture IA32 pour Intel Architecture 32 bits, et l’extension 64 bits x86-64 (Intel 64).

Il existe une famille IA64 Intel Itanium entre autres mais cette dernière n’est pas compatible avec IA32, et ne sera donc pas abordée.

Le deuxième grand type de processeur est construit sur l’architecture Harvard qui possède deux ensembles de bus pour les liaisons vers les zones de données et de code. Cette architecture est très différente de IA32, elle est adoptée par exemple pour les processeurs de traitement numérique, DSP (Digital Signal Processor).

Cette architecture permet de séparer le code et les données de manière physique, en les localisant dans deux composants de mémoire distincts, accédés par deux ensembles de bus distincts.

L’architecture des CPU x86 est toutefois plus puissante car elle permet par un mécanisme de segmentation et de pagination d’émuler de manière fiable et économique l’architecture Harvard. Tout en permettant un contrôle absolu sur toutes les données depuis un seul ensemble de bus.

La séparation matérielle du code et des données est donc virtuellement présente dans les CPU x86.

En réalité, le CPU n’est pas connecté directement aux périphériques et à la mémoire, cela passe par le chipset. Entre autres, le north bridge, qui s’occupe de la mémoire et des ports rapides, puis le south bridge, qui s’occupe...

Les modes du CPU

1. Le mode réel

Le mode réel 16 bits est le mode de démarrage du CPU, le mode par défaut.

En effet, par souci de rétrocompatibilité, tous les x86 démarrent dans ce mode.

Les restrictions du mode 16 bits pur sont très limitatives, néanmoins un CPU 32 bits reste capable d’interpréter les instructions 32 bits en mode 16 bits, ces instructions seront alors préfixées par les octets 66h, préfixe de registres, et 67h, préfixe d’adresse.

L’utilisation des registres et adresses 32 bits étant permise, il est possible de contourner les restrictions relatives aux instructions 16 bits.

Il faut tout de même évoquer quelles sont ces restrictions :

-

Les instructions du mode 16 bits sont en nombre limité.

-

Les registres utilisables en adressage sont limités à BX, SI, DI, BP et SP, registres d’index et de pointeurs.

-

Les multiplications et les divisions rencontrent des limitations.

Sur les CPU à partir du 386, les particularités du mode réel sont émulées par le biais des structures système du mode protégé et l’unité d’exécution.

2. Le mode protégé

Le mode protégé est le mode natif de tous les CPU 32 bits, mais ils ne peuvent pas démarrer en mode protégé en raison de la nature de ce mode...

Les registres x86

Tous les processeurs possèdent des registres, quelle que soit la famille ou l’architecture.

Comme évoqué précédemment, les registres sont à l’intérieur du CPU, et leur nombre est très limité.

L’utilisation des registres 16 bits est soumise à de sévères restrictions, tandis que les registres étendus 32 bits peuvent être utilisés indifféremment pour toutes les tâches d’adressage, de calcul, d’accumulation, etc.

1. Registres à usage général (GPR)

|

32 bits |

Bits 0 à 31 |

EAX |

EBX |

ECX |

EDX |

|

16 bits |

Bits 0 à 15 |

AX |

BX |

CX |

DX |

|

8 bits |

Bits 0 à 7 |

AL |

BL |

CL |

DL |

|

Bits 8 à 15 |

AH |

BH |

CH |

DH |

Ces registres sont destinés à exécuter toutes sortes d’opérations, telles que les additions, multiplications, indexations, affectations, tests...

mov eax,74289 ;mettre la valeur 74289 dans le registre eax Ils font 32 bits, sont accessibles dans leur partie basse 16 bits, qui à son tour est découpée en deux sous-parties 8 bits, ce qui permet d’accéder à une fraction du registre au lieu d’utiliser tout le registre.

En effet, il est tout à fait inutile de travailler sur un registre 32 bits pour une opération sur des données de 8 bits.

mov eax,012345678h;mettre la valeur 12345678h dans eax

mov al,90h ;modifier la valeur de AL Après l’instruction mov al,90h, EAX contient la valeur 12345690h, le contenu de AL étant changé, l’octet de poids faible de EAX l’est automatiquement.

Chacun des 4 registres généraux possède sa particularité :

-

Le registre EAX, à l’origine registre Accumulateur, est utilisé en registre de travail par défaut de nombreuses instructions de calcul.

-

Le registre EBX, à l’origine registre de Base, est utilisé comme référence pour des accès de tableaux.

-

Le registre ECX, à l’origine registre de Compteur, est utilisé pour les instructions répétitives et les opérations de décalages logiques.

-

Le registre EDX est utilisé comme registre de Données, extension du registre EAX, pour former le registre virtuel EDX:EAX ; il est aussi utilisé comme index lors des accès aux ports d’entrées/sorties....

Les extensions

1. FPU

Cette extension travaille sur des nombres en virgule flottante. La représentation flottante diffère du binaire pur et est définie par la norme IEEE 754.

L’extension FPU des processeurs x86 se nomme x87.

a. Les nombres flottants

Les nombres à virgule flottante peuvent être de 3 formats différents dans les CPU x86 :

32 bits : réel simple précisionIls peuvent représenter des nombres compris entre ±1,175494351×(10^-38) et ±3,4028235×(10^38).

La précision est de 6 décimales complètes (couvrant les chiffres 0 à 9 sur toutes les décimales).

Les bits 0 à 22 forment la mantisse.

Les bits 23 à 30 forment l’exposant.

Le bit 31 est le bit de signe.

64 bits : réel double précisionIls peuvent représenter des nombres compris entre ±2,2250738585072020×(10^-308) et ±1,7976931348623157×(10^308).

La précision est de 15 décimales complètes.

Les bits 0 à 51 sont utilisés pour la mantisse.

Les bits 52 à 62 sont utilisés pour l’exposant.

Le bit 63 est utilisé comme bit de signe.

80 bits : réel double précision étendueCette résolution est utilisée en interne dans la FPU uniquement.

Les nombres réels couvrent les nombres entre ±3.65×(10^4951) et ±1.19×10^(4932).

La précision est de 18 décimales complètes.

Les bits 0 à 62 représentent la mantisse.

Le bit 63 est toujours à 1 et représente le bit de poids fort de la mantisse.

Les bits 64 à 78 représentent l’exposant.

Le bit 79 est le bit de signe.

Un format supplémentaire existe dans la FPU x87, afin de charger des nombres décimaux.

80 bits : nombre BCD empaqueté de 18 chiffresIls peuvent représenter des nombres entiers compris entre 0 et ±999 999 999 999 999 999, soit des valeurs maximales de ±(10^19)-1 (un peu moins d’un milliard de milliards).

Le bit de poids fort (bit 79, ou bit 7 du dixième octet) est utilisé en tant que bit de signe.

Le reste du dixième octet est ignoré en raison de l’impossibilité de garder une telle précision avec les réels 80 bits.

Ce type de nombre est utilisé uniquement dans la RAM.

Le chargement...

La mémoire

La mémoire est le siège des données. Toutes les données transitent par la mémoire pour être traitées et enregistrées.

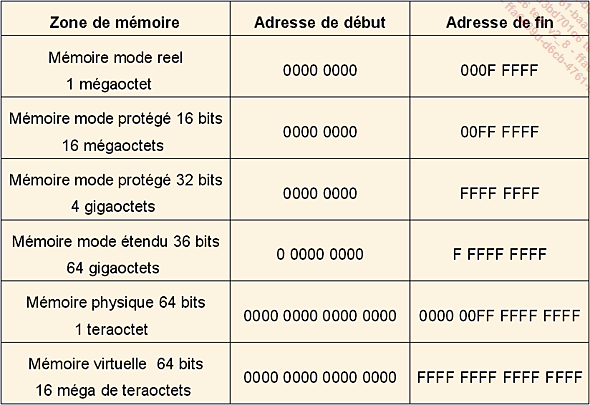

La mémoire d’un PC est accessible par le bus d’adresses et le bus de données. La zone de mémoire accessible varie en fonction du mode du processeur :

Zones de mémoire selon le mode du CPU

1. Plan général

Ce plan d’occupation de la mémoire ne s’applique qu’au mode réel et couvre uniquement le premier mégaoctet de l’espace d’adressage linéaire.

La mémoire au-dessus de 1 mégaoctet est entièrement disponible pour le CPU et la table de vecteurs d’interruption est inexistante, ce qui signifie qu’il faut d’abord initialiser les structures système avant de passer en mode protégé.

|

Plan de la mémoire |

||

|

Adresse linéaire |

Taille en octets |

Description |

|

0 |

1024 (400h) |

Table des vecteurs d’interruption en mode réel |

|

400h |

Zone de donnée du BIOS BDA |

|

|

7C00h |

512 (200h) |

Zone de chargement du secteur de BOOT |

|

0A0000h |

64k (10000h) |

Zone de mémoire vidéo en mode graphique, VGA |

|

0B8000h |

32k (08000h) |

Zone de mémoire vidéo en mode texte, VGA |

|

0FFFF0h |

Première instruction exécutée au démarrage du CPU |

|

|

100000h |

Mémoire étendue |

|

|

0 |

16 mégaoctets |

Mode protégé 16 bits, modèle 80286 |

|

4 gigaoctets |

Mode protégé 32 bits, 80386 et au-delà |

|

|

64 gigaoctets |

Extension IA32e |

|

|

1 téraoctet |

Mode 64 bits, bus limité à 40 bits |

|

Certains matériels accèdent eux aussi à la mémoire, comme par exemple le contrôleur DMA ou la carte graphique, ce qui réduit la liberté d’écriture en mémoire par le CPU. Il faut veiller à ne pas écrire dans la RAM avant d’être sûr de ne pas interférer avec le matériel.

Les zones assignées...

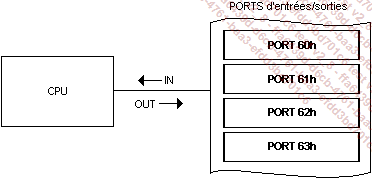

Les ports

Les ports d’entrées/sorties (I/O) sont les seuls liens directs du CPU vers l’extérieur.

Du point de vue matériel, les ports sont accédés lorsque le signal de contrôle I/O est actif, par les bus d’adresses et de données, de la même manière que la mémoire.

Il s’agit d’une sorte de mémoire constituée d’une succession de registres sur des périphériques, au lieu d’être une succession de cases mémoire dans les barrettes de RAM.

Les accès aux ports sont plus lents que les accès à la RAM, c’est pourquoi il est souvent fait usage de boucles ou de NOP lors de ces accès, mais leur utilisation n’est cependant par toujours obligatoire. Il y a lieu de procéder à des tests pour vérifier leur nécessité sur la machine de destination.

mov al,0 ;valeur à écrire dans al

mov dx,port_n ;port où écrire dans dx

out dx,al ;ordonner l'écriture au port pointé par dx

jmp $+2 ;équivalent à nop Le bus d’adresses est limité à 16 bits lors de l’accès aux ports.

Donc, théoriquement, il est possible d’accéder à 65536 ports dont le format...

Editions ENI Livres | Vidéos | e-Formations

Editions ENI Livres | Vidéos | e-Formations